-

AIX Exchange携手币安生态矩阵,揭幕“Web3版纳斯达克”

发布时间:2025/10/23

10月24日20:00,全球知名区块链媒体非小号(Feixiaohao.ai)、TalkingWeb3将携手AIXExchange和全球百大KOL举办华语区线上首秀特别直播,正式揭开“Web3版纳斯达克”的序幕。本次活动将在X、币安广场、币安Live、火...

-

撒钱十个亿,只做真公益!振东制药诠释现代公益新范式

发布时间:2025/06/11

如果说慈善事业是企业责任感的一个缩影。那么振东制药的慈善“侧写”便是大爱无疆。山西振东健康产业集团自太行山深处诞生,稳扎稳打、守正创新,跻身中国药企中流砥柱行列。引导旗下公益扶贫办凝聚共识、加强合作...

-

创客匠人联合主办第二届中国心理学应用发展大会,深耕“AI+心理学”应用

发布时间:2025/05/30

导语: 2025年5月24日,第二届中国心理学应用发展大会在杭州水博园盛大开幕。作为联合主办方,创客匠人通过“AI+心理学应用”圆桌论坛和“心理人的破局发展”工作坊两大核心活动,为3000余名参会者带来前沿的数字化解决方...

-

纳斯达克‖飞兔商联启航全产业链聚合生态重构行业格局

发布时间:2025/05/27

在互联网行业爆发式增长的浪潮中,贵州飞兔商联云信息技术有限公司(以下简称“飞兔商联”)以“科技+线上+线下”三位一体的合伙人创新模式,成为资本市场瞩目的焦点。作为中国互联网全产业链聚合生态的构建者,公司...

-

浑水协助Wolfpack做空爱奇艺(IQ.US) 看空报告全文来了

发布时间:2020/04/08

本文来源“腾讯网”。 划重点:1.两家中国广告公司向我们提供了爱奇艺(IQ.US)后端系统的数据,这些数据显示,从2019年9月开始,爱奇艺的实际移动DAU比该公司在2019年10月宣称的1.75亿平均移动DAU低了60.3%。2.大约3...

-

华尔街大佬巴鲁克:特斯拉(TSLA.US)目标股价达600美元,仍有18%上行空间

发布时间:2020/04/08

本文来自“腾讯证券”。 在券商杰富瑞(Jefferies)将特斯拉评级从“持有”上调到“买入”后,特斯拉(TSLA.US)在周一收盘上涨逾7.5%。上周五,特斯拉也因公司第一季度业绩强劲而迎来上涨。数据显示,该公司第一季度共...

-

不满足于流媒体业务,亚马逊也要开始做游戏了

发布时间:2020/04/08

本文来源“36氪”。为了在统治数字娱乐的战役中开辟新战线,Amazon(AMZN.US)正在投入数亿美元以成为视频游戏的领先制作商和发行商。由于卫生事件的影响数度推迟之后,这家互联网巨头表示,打算在5月发布其首款原创...

-

刘强东“熔断”,徐雷成为京东的新“保险丝”

发布时间:2020/04/08

本文来自“盒饭财经”。公共卫生事件笼罩世界,全球经济遭遇重创,金融市场难以幸免,“熔断”一词频繁走入人们视野中。 作为在美股上市的企业,京东(JD.US)最近的日子也不太好过。瑞幸造假事件曝出后,京东“二号人...

台积电(TSM.US)最新策略——砸钱

发布时间:2020/04/28 金融 浏览次数:853

本文来自 微信公众号“芯思想”。

2019年台积电(TSM.US)营收346.3亿美元,净利111.8亿美元,净利率高达32%。

2019年台积电晶圆出货量达1010万片12英寸晶圆约当量,2018年为1080万片12寸晶圆约当量;2019年先进制程技术(16/12/10/7纳米)的销售金额占整体晶圆销售金额的50%,高于2018年的41%;2019年在全球代工领域市场占有率达52%,高于2018年的51%。2019年提供272种不同的制程技术,为499个客户生产了10761种不同的芯片,应用范围包括整个电子应用产业,如个人电脑与其周边产品、信息应用产品、有线与无线通讯系统产品、服务器与数据中心、汽车与工业以及包括数字电视、游戏机、数码相机等消费性电子、物联网及穿戴式设备等。根据台积电方面的透露,目前台积电5纳米制程已经准备完成,随时可以进入到量产当中。在5纳米客户上,台积电目前几乎囊括了所有对于5纳米有需求的客户,包括苹果(Apple)、高通(Qualcomm)、海思(Hisilicon)、超微半导体(AMD)、联发科(MTK)等公司。3纳米技术继续使用FinFET晶体管结构,将于2021年试产,2022年量产;2019年已经投入2纳米研发,预计将于2024年投产。台积电真是越来越可怕,已经成为晶圆代工市场的巨无霸。下面芯思想研究院从三个方面解析台积电。

大手笔研发投入,助力技术领先2000年研发费用首次超过1亿美元,2007年研发费用首次突破5亿美元,2011年研发费用首次突破10亿美元,2015年研发费用首次突破20亿美元;2019年研发费用为29.6亿美元,接近30亿美元。从2000年到2019年研发费用合计达240亿美元,而从2015年到2019年的研发费用合计128亿美元,超过前15年的研发费用总和。大手笔研发投入带来的是技术的领先。2018年台积电的财报中有一句话:成功地量产7纳米(N7)制程,并领先其他同业至少一年。2019年6月台积电成功量产7纳米加强版(N7+),这是业界首个商用极紫外光(EUV)制程。此举意义重大。这是台积电历史上第一次在一个重要技术节点,领先群雄。根据英特尔的技术路线图,EUV要到20201年才会导入,这表明台积电领先英特尔至少两年。在FinFET工艺之争中,英特尔于2011年成功推出22纳米Tri-Gate技术,台积电直到2015年才推出16纳米FinFET工艺,整整晚了四年。台积电自1987年透过转让台湾工业技术研究院的2微米和3.5微米工艺技术创立公司,一直秉持“内部研发”战略,并在当年为飞利浦定制了3.0微米工艺技术;1988年,刚刚一岁的台积电就自研了1.5微米工艺技术;1999年发布了世界上第一个0.18微米低功耗工艺技术;2003年推出了当时业界领先的0.13微米低介质铜导线逻辑制程技术;2004年全球首家采用浸没式光刻工艺生产90纳米芯片;2006年量产65纳米工艺技术;2008年量产40纳米工艺技术;2011年全球首家推出28纳米通用工艺技术;2014年全球首家量产20纳米工艺技术。台积电在开始20纳米制程研发时,就瞄准布局FinFET,2012年完成16纳米制程的定义,迅速且顺利地完成测试芯片的产品设计定案,并在以FinFET架构为基础的静态随机存取存储器单位元(SRAM Bit Cell)上展现功能性良率;并在2014年开始风险生产16FF+工艺,2015年就顺利量产;2016年采用多重曝光的10纳米工艺也迅速进入量产,量产速度较之前的制程更快。台积电的7纳米是10纳米的缩小版(shrink),后部金属工艺技术基本兼容,整体密度和性能改进不多。采用DUV加浸没式(immersion)和多重图案(multiple patterning)方案的7纳米于2017年4月开始风险生产,,2018年第三季开始贡献营收,在2018年有40多个客户产品流片,2019年有100多个新产品流片。与10纳米FinFET工艺相比,7纳米FinFET具有1.6倍逻辑密度,约20%的速度提升和约40%的功耗降低。有两个工艺制程可选,一是针对AP(N7P),二是针对HPC(N7HP)。联发科天玑1000、苹果A13和高通骁龙865都是采用N7P工艺。台积电第一个使用极紫外光(EUV)方案的工艺是7纳米加强版(N7+)。N7+于2018年8月进入风险生产阶段,2019年第三季开始量产,N7+的逻辑密度比N7提高15%至20%,同时降低功耗。7纳米之后是6纳米(N6)。2019年4月份推出的6纳米是7纳米的(shrink),设计规则与N7完全兼容,使其全面的设计生态系统得以重复使用,且加速客户产品上市时间,但N6的逻辑密度比N7高出18%的。N6将在2020年第一季风险试产,第三季实现量产。7纳米之后的全节点提升的工艺是5纳米(N5)。5纳米完全采用极紫外光(EUV)方案,于2019年3月进入风险生产阶段,预期2020年第二季拉高产能并进入量产。主力生产工厂是Fab 18。与7纳米制程相较,但5纳米从前到后都是全新的节点,逻辑密度是之前7纳米的1.8倍,SRAM密度是7纳米的1.35倍,可以带来15%的性能提升,以及30%的功耗降低。5纳米的另一个工艺是N5P,预计2020年第一季开始试产,2021年进入量产。与5nm制程相较在同一功耗下可再提升7%运算效能,或在同一运算效能下可再降低15%功耗。5纳米之后的全节点提升的工艺是3纳米,台积电表示正在研发中,虽然制程细节2020年4月将见分晓。但根据一些细节发现,台积电3纳米工艺继续采用FinFET工艺,晶体管密度达到每平方毫米2.5亿个(250MTr/mm2),相对于5纳米来说,晶体管密度提升达1.5倍,性能提升7%,能耗减少15%。

而2纳米,台积电表示已经于2019年领先半导体产业进行制程技术的研发,并将着重于改善极紫外光(EUV)技术的质量与成本。

大规模资本支出,扩大产能日前,台积电宣布,2020年的资本支出将在150-160亿美元之间,这将成为台积电资本支出最大的一年。

2000年资本支出首次超过10亿美元,2010年资本支出首次超过50亿美元,2016年资本支出首次超过100亿美元。从2000年到2019年资本支出合计达1150亿美元,而从2016年到2019年的资本支出是464亿美元,占近20年资本支出总和的40%。大规模资本支出带来的是庞大的产能支持。

截至2019年底,台积电全球有五座12英寸晶圆厂(新竹FAB12、台南FAB14、台中FAB15、南京FAB16、台南FAB18)、六座8英寸晶圆厂(新竹FAB3、新竹FAB5、新竹FAB6、新竹FAB8、上海FAB10、美国FAB11)和一座6英寸晶圆厂(新竹FAB2),年产能超过1200万片12英寸晶圆约当量。  我们下面来了解一下台积电的FinFET产能建置情况。

我们下面来了解一下台积电的FinFET产能建置情况。

台积电最早生产FinFET始于2014年,目前FinFET工艺有5个基地,分别是位于台湾新竹的FAB12、台湾台南的FAB14和FAB18、台湾台中的FAB15和江苏南京的FAB16。各工艺节点的布局是,16/12纳米由FAB14和FAB16负责生产,合计月产能约15万片;7纳米由FAB15负责生产,合计月产能约15万片;5纳米主要在FAB18生产,目前FAB18 P1/P2的建置产能达10万片。

当然FAB12是台积电的研发基地,各工艺节点的产能都可以协调。如此算来,台积电的FinFET月产能总计不下于40万片12英寸晶圆。相较三星的月产能25万片12英寸晶多60%

关于3纳米产能建置情况,因公共卫生事件导致物流延迟,相关关键设备无法如期交货,装机人员也受到境外人士不能抵台等限制,无法如期装机。台媒报道称,FAB12B工厂3纳米试产线装机从6月延至10月,FAB18工厂3纳米试产线装机从10月也将延迟1个季度。台积电原订今年底提前试产3nm制程计划,将延至明年初才会试产,但应会如原先预定在2022年量产。

至于在3纳米工艺上的资金投入更是天文数字,据称研发和建线已投入约500亿美元,仅建厂一项就在200亿美元。3纳米产线将于2020年动工,在新竹宝山兴,建预计投资超过新台币6000亿元兴建3纳米宝山厂,最快2022年底量产。

还有就是从2010年开始,台积电从ASML购得第一台EUV(第一代EUV机型NXE: 3100)至今,台积电拥有超过30台EUV光刻机,约占全球EUV光刻机总出货量的一半。这也是台积电产能保障的一部分。

布局高端封装,形成客户粘性2008年开始先进封装布局。首先成立集成互连与封装技术整合部门,2009年开始战略布局三维集成电路(3D IC)系统整合平台。在新竹、台南、桃园、台中建有四座先进封测厂。

目前,台积电先进封装技术WLSI(Wafer-Level-System-Integration)平台包括既有的CoWoS封装、InFO封装,以及针对物联网芯片的晶圆级封装(WLCSP),还将于2021年推出系统级整合芯片(SoIC,System-on-integrated-chips)封装技术,阵容更加齐整、坚强。

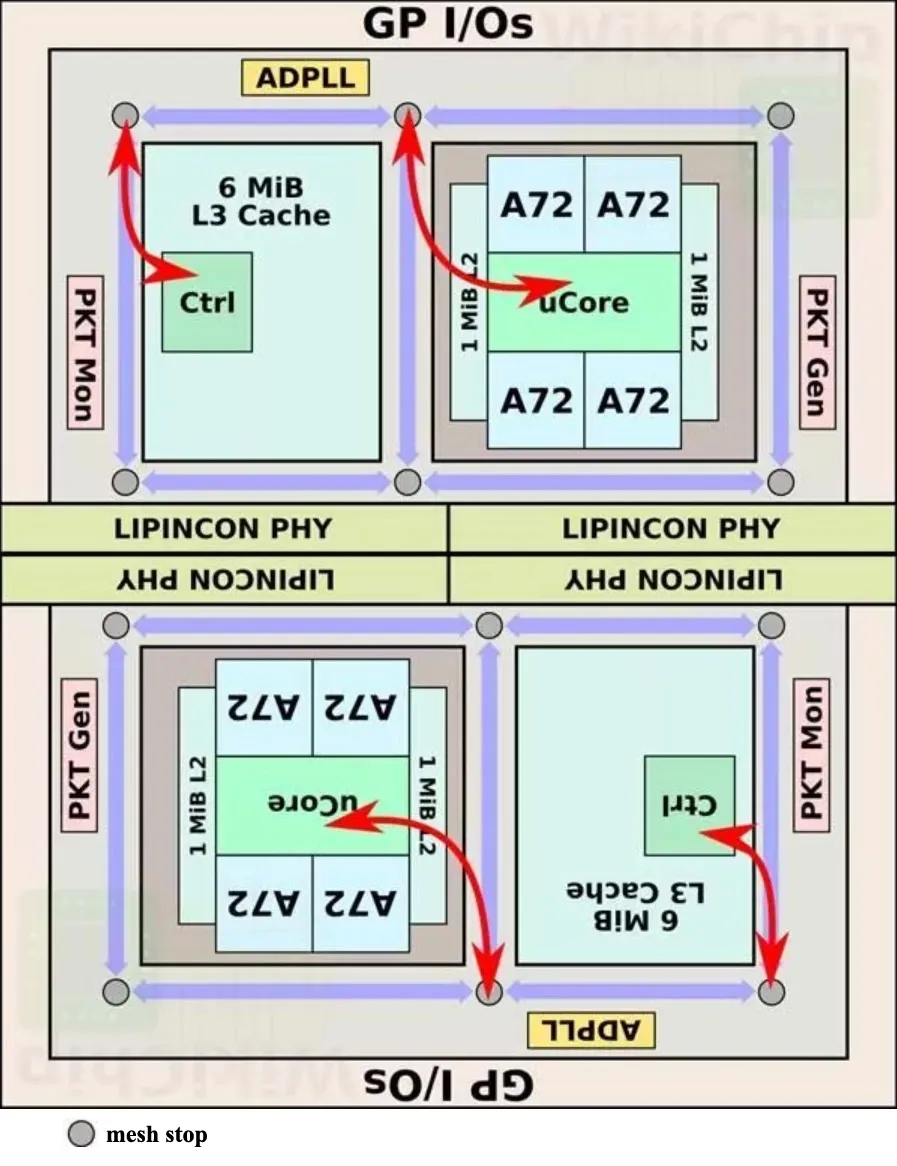

1、CoWoSCoWoS主要针对高性能计算(High Performance Computing,HPC)市场。2011年推出2.5D Interposer技术CoWoS(Chip on Wafer on Substrate,晶圆基底封装)。张忠谋在第三季法说会上放言,台积电要进军封装领域。此举震撼半导体业界,特别是封装业界。第一代CoWoS采用65纳米工艺,线宽可以达到0.25µm,实现4层布线,为FPGA、GPU等高性能产品的集成提供解决方案。到2013年量产时,可编程逻辑门阵列供应赛灵思(Xilinx)型号为“Virtex-7 2000T FPGA”的28纳米产品是最具代表性的CoWoS产品之一。目前CoWoS已经获得赛灵思(Xilinx)、英伟达(nVIDIA)、超微半导体(AMD)、富士通(Fujitsu)谷歌(Google)、华为海思(HiSilicon)等高端HPC芯片订单。 2019年第三季CoWoS技术目前已经扩展至7纳米,能够在尺寸达二倍光罩大小的硅基板(Silicon Interposer)上异质整合多颗7纳米系统单晶片与第二代高频宽存储器(High Bandwidth Memory 2,HBM2)。值得注意的是,在VLSI Symposium会上,台积电展示了自己为高性能计算平台设计的一颗名为“This”小芯片(Chiplet),采用7纳米工艺,面积大小仅仅27.28平方毫米(4.4×6.2mm),采用CoWos封装技术,双芯片结构,其一内建4个Cortex A72核心,另一内建6MiB三级缓存。This的标称最高主频为4GHz,实测达到了4.2GHz(1.375V)。同时,台积电还开发了称之为LIPINCON互连技术,信号数据速率8 GT/s。 2、InFO

2、InFO

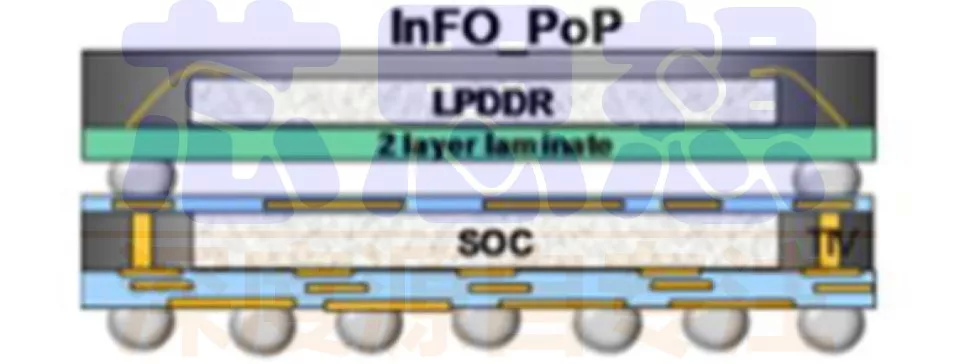

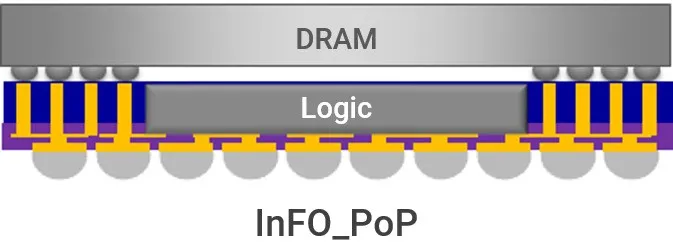

InFO技术成功应用于追求高性价比的移动通讯市场,AP产品是其主要客户。2016年台积电推出的InFO技术是最具代表性的扇出封装技术,InFO带动了整个业界研发三维扇出堆叠技术的热潮。 InFO是将CoWoS结构尽量简化,最后出来一个无须硅中介层的精简设计,可以让芯片与芯片之间直接连结,减少厚度,成本也相对较CoWoS低廉,但又能够有良好的表现,适用于追求性价比的移动通信领域,在手机处理器封装中,减低30%的厚度,腾出宝贵的手机空间给电池或其他零件。这就是2016年首次开始在苹果的A10处理器中采用InFO封装,首度用在苹果iPhone 7与iPhone 7Plus中。InFO成为台积电独占苹果A系列处理器订单的关键。 图1 台积电InFO技术图1展示了台积电InFO技术,通过将芯片埋入模塑料,以铜柱实现三维封装互连。InFO技术为苹果A10、A11、A12处理器和存储器的PoP封装提供了新的封装方案,拓展了WL-FO的应用,让Fan-Out技术成为行业热点。

图1 台积电InFO技术图1展示了台积电InFO技术,通过将芯片埋入模塑料,以铜柱实现三维封装互连。InFO技术为苹果A10、A11、A12处理器和存储器的PoP封装提供了新的封装方案,拓展了WL-FO的应用,让Fan-Out技术成为行业热点。

台积电InFO技术的成功得益于强大的研发能力和商业合作模式。推出InFO技术,是为了提供AP制造和封装整体解决方案,即使在最初良率很低的情况下,台积电也能持续进行良率提升,这对封测厂来说是不可能的。

InFO技术的巨大成功推动制造业、封测业以及基板企业投入了大量人力物力开展三维扇出技术的创新研发。业界也发现,很多原本需要2.5D TSV转接板封装可以通过三维扇出来完成,解决了TSV转接板成本太高,工艺太复杂的问题。

根据不同产品类别,台积电的InFO技术发展也将随之进行调整,推出适用于HPC(High Performance Computer)高效能运算电脑的InFO-oS(InFO on substrate)、服务器及存储器的(InFO Packageon-Package,InFO-PoP),以及5G通讯天线封装方面的InFO-AiP(InFO Antennas in Packag)。 InFO-oS

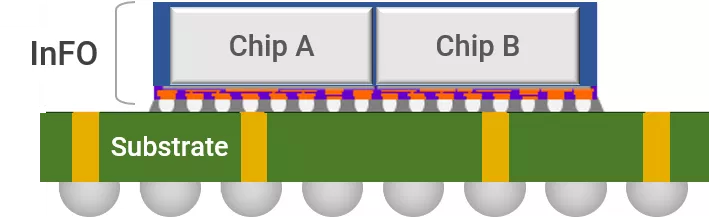

InFO-oS 2018年台积电推出InFO_oS技术用于并排封装两个芯片,芯片与芯片之间的互连为2um。芯片之间的间隙小于70um;InFO_MS和InFO_oS基本相同,但在SoC旁边带有HBM(高带宽内存)。

2018年台积电推出InFO_oS技术用于并排封装两个芯片,芯片与芯片之间的互连为2um。芯片之间的间隙小于70um;InFO_MS和InFO_oS基本相同,但在SoC旁边带有HBM(高带宽内存)。

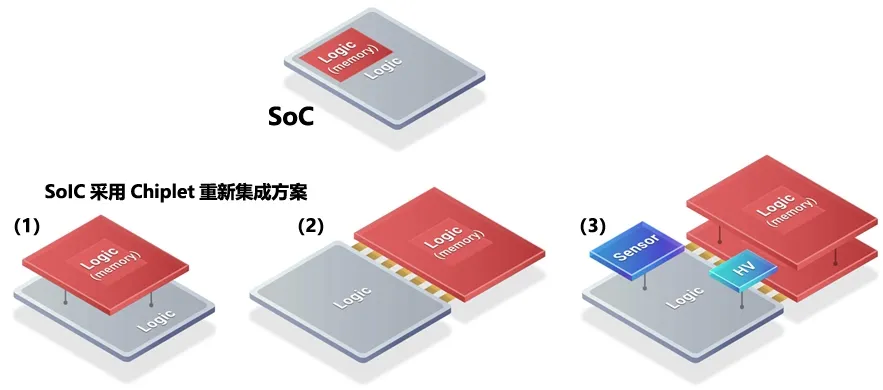

3、SoIC台积电表示,SoIC是一种创新的多芯片堆叠技术,是一种将带有TSV的芯片通过无凸点混合键合实现三维堆叠,可以交多个小芯片(Chiplet)整合成一个面积更小和轮廓更薄的系统单芯片。透过此项技术,7纳米、5纳米甚至3纳米的先进系统单芯片能够与多阶层、多功能芯片整合,可实现高速、高频、低功耗、高间距密度、最小占用空间的异质三维集成电路。 SoIC技术的出现表明未来的芯片能在接近相同的体积里,增加双倍以上的性能。这意味着SoIC技术可望进一步突破单一芯片运行效能,更可以持续维持摩尔定律。据悉SoIC根植于台积电的CoWoS与多晶圆堆叠(WoW,Wafer-on-Wafer)封装,SoIC特别倚重于CoW(Chip-on-wafer)设计,如此一来,对于芯片业者来说,采用的IP都已经认证过一轮,生产上可以更成熟,良率也可以提升,也可以导入存储器芯片应用。2019年年报显示,台积电已完成SoIC制程认证,开发出微米级接合间距(bonding pitch)制程,并获得极高的电性良率与可靠度数据,具备为任何潜在客户用生产的能力。而此前在2018年10月的第三季法说会上,台积电给出了明确量产的时间,2021年SoIC技术就将进行量产。

SoIC技术的出现表明未来的芯片能在接近相同的体积里,增加双倍以上的性能。这意味着SoIC技术可望进一步突破单一芯片运行效能,更可以持续维持摩尔定律。据悉SoIC根植于台积电的CoWoS与多晶圆堆叠(WoW,Wafer-on-Wafer)封装,SoIC特别倚重于CoW(Chip-on-wafer)设计,如此一来,对于芯片业者来说,采用的IP都已经认证过一轮,生产上可以更成熟,良率也可以提升,也可以导入存储器芯片应用。2019年年报显示,台积电已完成SoIC制程认证,开发出微米级接合间距(bonding pitch)制程,并获得极高的电性良率与可靠度数据,具备为任何潜在客户用生产的能力。而此前在2018年10月的第三季法说会上,台积电给出了明确量产的时间,2021年SoIC技术就将进行量产。

4、其他针对先进行动装置及高效能运算的应用,采用细小间距阵列铜凸块(Cu bump)倒装(Flip Chip)的7纳米晶圆已于2018年第一季开始量产。除了高阶先进手 机内使用的28 奈米产品及更成熟技术外, 适用于物 联网应用的16 奈米制程的晶圆级封装(Wafer Level Chip Scale Packaging, WLCSP)技术亦于民国一百零 七年第四季开始量产。台积电的CoWoS、InFO、SoIC及其他封装技术能对10纳米或以下的制程进行晶圆级的键合技术,极大的强化台各积电在先进工艺制程的竞争力。台积电除了提供内部CoWoS和InFO服务外,还通过外包的组装和测试合作伙伴管理整个供应链,从而为客户提供集成的制造、封测、运输的交钥匙服务,帮助客户缩短上市时间和缩短批量生产时间。(编辑:杨杰)